지멘스 디지털 인더스트리 소프트웨어, 지멘스 EDA 사업부 (http://www.siemens.com/eda)는 2.5D 및 3D 아키텍처 기반 차세대 IC의 중요 DFT(Design-for-Test: 설계단계에서 칩의 공정상 결함이 있는지 체크) 작업 속도를 극대화할 수 있는 테센트 멀티-다이(Tessent™ Multi-die) 소프트웨어 솔루션을 20일 발표했다.

차세대 디바이스는 갈수록 더 복잡한 2.5D 및 3D 아키텍처를 채택하는 추세다. 이러한 아키텍처는 다이를 수직 연결하거나(3D IC) 병렬 연결해(2.5D) 단일 디바이스처럼 동작하도록 한다. 하지만 이러한 접근 방식은 IC 테스트에서 중요한 문제에 봉착할 수 있다. 대부분의 레거시 IC 테스트 접근방식은 기존의 2차원적 프로세스를 기반으로 하기 때문이다.

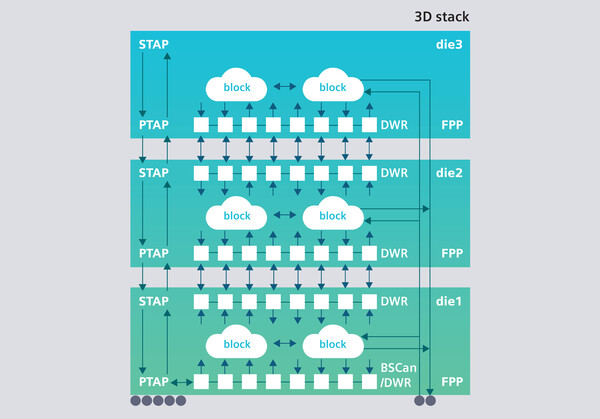

이같은 문제를 해결하기 위해 지멘스가 선보인 Tessent Multi-die 소프트웨어는 2.5D 및 3D IC 설계와 관련된 복잡한 DFT 작업을 수행하기 위한 포괄적인 DFT 자동화 솔루션이다. 이 Tessent Multi-die 솔루션은 지멘스의 Tessent™ TestKompress™ Streaming Scan Network 소프트웨어 및 Tessent™ IJTAG 소프트웨어와 완벽하게 연동된다. 이 소프트웨어들은 설계의 나머지 부분에 미칠 수 있는 영향 없이 각 블록에 대한 DFT 테스트 리소스를 최적화하므로 2.5D 및 3D IC 시대의 DFT 계획과 구현이 간소화된다. IC 설계 팀은 Tessent Multi-die 소프트웨어를 사용하여 2.5D 및 3D IC 아키텍처를 갖는 IEEE 1838 호환 하드웨어를 신속하게 생성할 수 있다.

Tessent Multi-die 솔루션은 2.5D 및 3D IC 설계에 대한 포괄적인 테스트를 지원하는 것 외에도 다이간 인터커넥트 패턴을 생성할 수 있으며, BSDL(Boundary Scan Description Language)을 사용해 패키지 레벨의 테스트를 수행할 수 있다. 또한 Tessent Multi-die 솔루션은 지멘스의 Tessent TestKompress Streaming Scan Network 소프트웨어의 패킷화된 데이터 전송 기능을 활용하여 FPP(Flexible Parallel Port) 기술의 통합도 지원한다.

2년전 선보인 Tessent TestKompress Streaming Scan Network는 코어 레벨의 DFT 요건을 칩 레벨의 테스트 시행 리소스로부터 분리시킨다. 이를 통해 성능 저하 없는 상향식의 DFT 흐름이 가능해진다. 이는 DFT 계획 및 구현을 극적으로 간소화하는 동시에 테스트 시간도 최대 4배까지 단축할 수 있다.