IBM과 삼성전자가 반도체 트랜지스터에서 전류가 수직 방향으로 흐르는 VTFET(Vertical Transport Field Effect Transistors) 기술을 개발했다. 이를 통해 한정된 반도체 공간 내에 더 많은 수의 트랜지스터를 내장하고, 기존 핀펫(finFET) 대비 최대 85%의 전력을 절감할 수 있다고 발표했다.

컨테이너 수직으로 세워 공간을 절감하는 구조

IBM과 삼성전자는 수직 구조의 트랜지스터가 적용된 VTFET를 개발했다고 15일 밝혔다. VTFET은 이전에 낸드플래시 메모리가 수평으로 제조되다가 수직으로 구조를 변경한 것과 유사한 접근 방식이다.

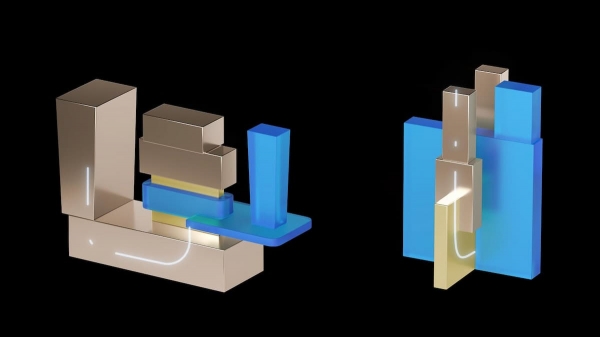

반도체는 소스와 드레인 사이 전류 흐름을 통해 연산하거나 정보를 저장하는데, 그동안 소스-드레인은 실리콘 웨이퍼에 수평 방향으로 형성됐다. 이 소스-드레인 사이의 거리를 좁혀줘야 반도체 전력효율이 높아지고, 동일한 면적에 더 많은 수의 트랜지스터를 내장할 수 있는데 현재는 이 방식이 한계에 봉착했다. EUV(극자외선)를 이용한 미세공정의 발전에도 더 이상 소스-드레인 사이의 거리를 좁힐 수 없을 만큼 가까워진 탓이다.

VTFET은 소스-드레인을 웨이퍼의 수직 방향으로 세워 이 같은 문제를 해결하려는 시도다. 전류 흐름 제어를 위해 최소한의 거리를 유지해야 했던 소스-드레인을 세로로 배치함으로써 트랜지스터의 물리적 부피를 줄일 수 있다. 좁은 야적장에 컨테이너 박스를 보관한다고 가정하면, 일반적인 수평으로 놓는것 보다 수직으로 세워 보관할 때 더 많은 컨테이너를 보관할 수 있는 것과 유사하다.

IBM은 이와 함께 삼성전자⋅TSMC⋅인텔이 차기 공정으로 개발하고 있는 GAA(Gate All Around) 구조도 VTFET에 가미했다. 이날 IBM이 공개한 VTFET 개략도를 보면 소스-드레인 사이의 채널을 게이트가 4면으로 둘러싼 형태를 확인할 수 있다.

IBM측은 “VTFET 공정은 한정된 면적에 더 많은 트랜지스터를 집적할 수 있게 하며, 트랜지스터의 접점을 개선해 전류 낭비를 줄인다”며 “기존 핀펫 공정 칩 대비 2배 높은 성능 또는 전력 사용량을 85% 절감할 수 있다”고 강조했다.

이날 IBM과 삼성전자는 VTFET을 언제 어느 제품에 적용할 지에 대해서는 언급하지 않았다. 다만 최근 IBM이 기존 기술로 2nm(나노미터) 공정을 구현했다고 발표한 만큼, VTFET는 2nm 대비 더 진보된 제품에 첫 적용될 것으로 보인다. 반도체 업계는 2nm 공정 양산 시점을 2025년 정도로 본다. 계산대로라면 VTFET 상용화는 빨라도 2026년, 혹은 그 이후가 되는 셈이다.

한 글로벌 반도체 업체 임원은 “소스-드레인을 수직으로 세워 면적을 절감하는 컨셉트 자체는 이미 여러 연구가 진행되어 왔다”며 “이를 양산 공정에서 얼마나 안정적으로 구현할 수 있느냐가 관건”이라고 말했다.